izdelki kategorija

- FM oddajnik

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV oddajnik

- 0-50w 50-1kw 2kw-10kw

- FM antene

- TV Antenna

- Antenna pripomočki

- Cable priključek moč Splitter Dummy Load

- RF Transistor

- Napajanje

- avdio oprema

- DTV Front End oprema

- Link sistem

- STL sistem Sistem Mikrovalovna Link

- FM radio

- power Meter

- Ostali izdelki

- Posebno za koronavirus

izdelki Oznake

Fmuser strani

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikanščina

- sq.fmuser.net -> albanski

- ar.fmuser.net -> arabščina

- hy.fmuser.net -> Armenščina

- az.fmuser.net -> azerbajdžanski

- eu.fmuser.net -> baskovščina

- be.fmuser.net -> belorusko

- bg.fmuser.net -> bolgarščina

- ca.fmuser.net -> katalonščina

- zh-CN.fmuser.net -> kitajščina (poenostavljena)

- zh-TW.fmuser.net -> kitajščina (tradicionalno)

- hr.fmuser.net -> hrvaški

- cs.fmuser.net -> češčina

- da.fmuser.net -> danski

- nl.fmuser.net -> nizozemščina

- et.fmuser.net -> estonščina

- tl.fmuser.net -> filipinsko

- fi.fmuser.net -> finski

- fr.fmuser.net -> francosko

- gl.fmuser.net -> galicijščina

- ka.fmuser.net -> gruzijski

- de.fmuser.net -> nemščina

- el.fmuser.net -> grščina

- ht.fmuser.net -> haitijska kreolščina

- iw.fmuser.net -> hebrejščina

- hi.fmuser.net -> hindujščina

- hu.fmuser.net -> madžarščina

- is.fmuser.net -> islandski

- id.fmuser.net -> indonezijski

- ga.fmuser.net -> irski

- it.fmuser.net -> italijanščina

- ja.fmuser.net -> japonski

- ko.fmuser.net -> korejski

- lv.fmuser.net -> latvijski

- lt.fmuser.net -> litovščina

- mk.fmuser.net -> makedonščina

- ms.fmuser.net -> malajščina

- mt.fmuser.net -> malteščina

- no.fmuser.net -> norveščina

- fa.fmuser.net -> perzijski

- pl.fmuser.net -> poljščina

- pt.fmuser.net -> portugalščina

- ro.fmuser.net -> romunščina

- ru.fmuser.net -> ruščina

- sr.fmuser.net -> srbščina

- sk.fmuser.net -> slovaški

- sl.fmuser.net -> slovenščina

- es.fmuser.net -> španščina

- sw.fmuser.net -> svahili

- sv.fmuser.net -> švedščina

- th.fmuser.net -> tajska

- tr.fmuser.net -> turški

- uk.fmuser.net -> ukrajinski

- ur.fmuser.net -> urdujščina

- vi.fmuser.net -> Vietnamščina

- cy.fmuser.net -> valižanščina

- yi.fmuser.net -> jidiš

PMOS in NMOS tranzistorji

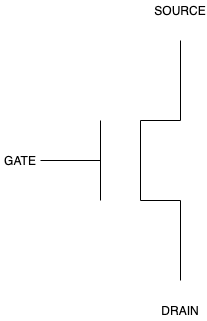

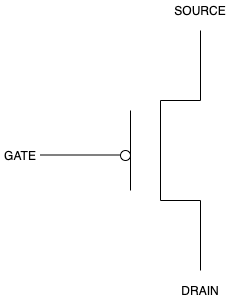

Mikroprocesorji so zgrajeni iz tranzistorjev. Zlasti so izdelani iz MOS tranzistorjev. MOS je kratica za Metal-Oxide Semiconductor. Obstajata dve vrsti MOS tranzistorjev: pMOS (pozitivni MOS) in nMOS (negativni MOS). Vsak pMOS in nMOS je opremljen s tremi glavnimi komponentami: vrata, vir in odtok.

Da bi pravilno razumeli, kako delujeta pMOS in nMOS, je pomembno najprej opredeliti nekaj izrazov:

zaprt krog: to pomeni, da električna energija teče od vrat do vira.

odprt krog: to pomeni, da električna energija ne teče od vrat do vira; ampak elektrika teče od vrat do odtoka.

Ko nMOS tranzistor prejme nezanemarljivo napetost, povezava od vira do odtoka deluje kot žica. Električna energija bo od vira do odtoka tekla neovirano - to se imenuje zaprt krog. Po drugi strani pa, ko nMOS tranzistor prejme napetost pri približno 0 voltov, bo povezava od vira do odtoka prekinjena in to se imenuje odprto vezje.

Tranzistor p-tipa deluje popolnoma v nasprotju s tranzistorjem n-tipa. Medtem ko bo nMOS tvoril zaprt tokokrog z virom, ko napetost ni zanemarljiva, bo pMOS tvoril odprt tokokrog z virom, ko napetost ni zanemarljiva.

Kot lahko vidite na zgornji sliki pMOS tranzistorja, je edina razlika med pMOS tranzistorjem in nMOS tranzistorjem majhen krog med vrati in prvo palico. Ta krog obrne vrednost iz napetosti; Torej, če vrata pošljejo napetost, reprezentativno za vrednost 1, bo pretvornik spremenil 1 v 0 in povzročil ustrezno delovanje vezja.

Ker pMOS in nMOS delujeta na nasproten način - na komplementaren način -, ko oba združimo v eno velikansko MOS vezje, se imenuje cMOS vezje, kar pomeni komplementarni kovinsko-oksidni polprevodnik.

Uporaba MOS vezij

Lahko kombiniramo pMOS in nMOS vezja, da bi zgradili bolj zapletene strukture, imenovane GATES, natančneje: logična vrata. Koncept teh logičnih funkcij in z njimi povezanih tabel resnic smo že predstavili v prejšnjem blogu, ki ga najdete s klikom tukaj.

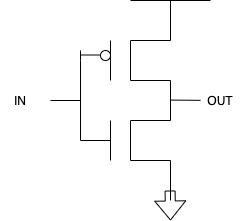

Lahko pritrdimo pMOS tranzistor, ki se poveže z virom, in nMOS tranzistor, ki se poveže z zemljo. To bo naš prvi primer cMOS tranzistorja.

Ta cMOS tranzistor deluje na podoben način kot logična funkcija NOT.

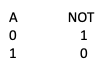

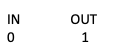

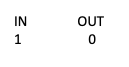

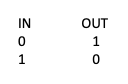

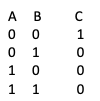

Oglejmo si tabelo NI resnice:

V tabeli resnice NOT je vsaka vhodna vrednost: A obrnjena. Kaj se zgodi z zgornjim vezjem?

No, predstavljajmo si, da je vnos 0.

0 vstopi in gre tako navzgor kot navzdol po žici do pMOS (zgoraj) in nMOS (spodaj). Ko vrednost 0 doseže pMOS, se obrne na 1; torej je povezava z virom zaprta. To bo ustvarilo logično vrednost 1, če tudi povezava z ozemljitvijo (odtok) ni zaprta. No, ker so tranzistorji komplementarni, vemo, da nMOS tranzistor ne bo obrnil vrednosti; torej vzame vrednost 0 takšno, kot je, in bo zato ustvaril odprt tokokrog do tal (odtok). Tako se za vrata ustvari logična vrednost 1.

Kaj se zgodi, če je 1 vrednost IN? No, po istih korakih kot zgoraj, se vrednost 1 pošlje tako pMOS kot nMOS. Ko pMOS prejme vrednost, se vrednost obrne na 0; tako je povezava z VIROM odprta. Ko nMOS prejme vrednost, se vrednost ne obrne; tako ostane vrednost 1. Ko nMOS prejme vrednost 1, se povezava zapre; torej je povezava z zemljo zaprta. To bo ustvarilo logično vrednost 0.

Če združimo dva niza vhoda/izhoda, dobimo:

Precej enostavno je videti, da je ta tabela resnice popolnoma enaka tisti, ki jo logična funkcija NE proizvaja. Tako je to znano kot vrata NE.

Ali lahko uporabimo ta dva preprosta tranzistorja za izdelavo bolj zapletenih struktur? Vsekakor! Nato bomo zgradili vrata NOR in vrata ALI.

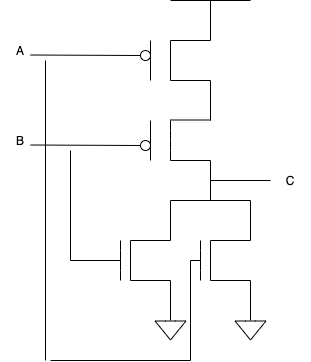

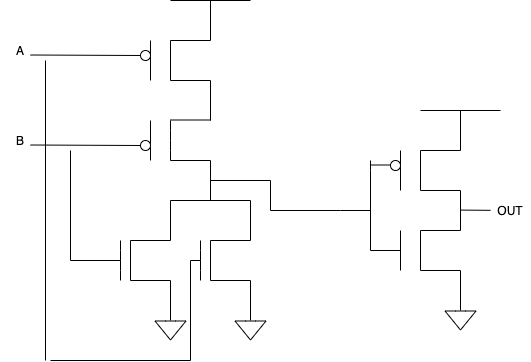

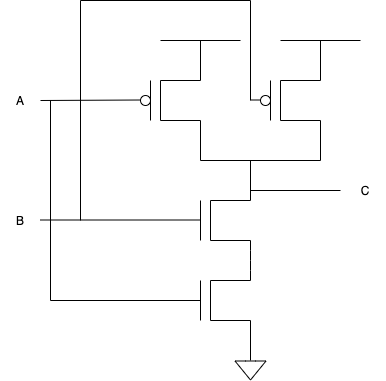

To vezje uporablja dva pMOS tranzistorja na vrhu in dva nMOS tranzistorja na dnu. Še enkrat, poglejmo vhod v vrata, da vidimo, kako se obnaša.

Ko je A 0 in je B 0, bodo ta vrata obrnila obe vrednosti v 1, ko dosežeta pMOS tranzistorje; vendar bosta oba tranzistorja nMOS ohranila vrednost 0. To bo vodilo do tega, da bodo vrata ustvarila vrednost 1.

Ko je A 0 in B 1, bodo ta vrata obrnila obe vrednosti, ko dosežeta pMOS tranzistorje; tako se bo A spremenil v 1 in B se bo spremenil v 0. To ne bo vodilo do vira; ker oba tranzistorja zahtevata zaprto vezje, da povežeta vhod z virom. Tranzistorji nMOS ne obrnejo vrednosti; tako bo nMOS, povezan z A, ustvaril 0, nMOS, povezan z B, pa bo ustvaril 1; tako bo nMOS, povezan z B, ustvaril zaprto vezje do tal. To bo vodilo do tega, da bodo vrata ustvarila vrednost 0.

Ko je A 1 in je B 0, bodo ta vrata obrnila obe vrednosti, ko dosežeta pMOS tranzistorje; tako se bo A spremenil v 0 in B se bo spremenil v 1. To ne bo vodilo do vira; ker oba tranzistorja zahtevata zaprto vezje, da povežeta vhod z virom. Tranzistorji nMOS ne obrnejo vrednosti; tako bo nMOS, povezan z A, ustvaril 1, nMOS, povezan z B, pa bo ustvaril 0; tako bo nMOS, povezan z A, ustvaril zaprto vezje do tal. To bo vodilo do tega, da bodo vrata ustvarila vrednost 0.

Ko je A 1 in B 1, bodo ta vrata obrnila obe vrednosti, ko dosežeta pMOS tranzistorje; tako se bo A spremenil v 0 in B se bo spremenil v 0. To ne bo vodilo do vira; ker oba tranzistorja zahtevata zaprto vezje, da povežeta vhod z virom. Tranzistorji nMOS ne obrnejo vrednosti; tako bo nMOS, povezan z A, ustvaril 1, nMOS, povezan z B, pa bo ustvaril 1; tako bosta nMOS, povezana z A, in nMOS, povezana z B, ustvarila zaprto vezje z zemljo. To bo vodilo do tega, da bodo vrata ustvarila vrednost 0.

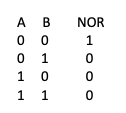

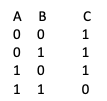

Tako je tabela resnice vrat naslednja:

Medtem je tabela resnice logične funkcije NOR naslednja:

Tako smo potrdili, da so ta vrata vrata NOR, ker delijo svojo tabelo resnice z logično funkcijo NOR.

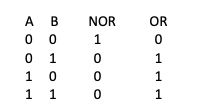

Zdaj bomo združili oba vrata, ki smo jih do sedaj ustvarili, da bi ustvarili vrata ALI. Ne pozabite, NOR pomeni NE ALI; torej, če obrnemo že obrnjena vrata, bomo dobili nazaj izvirnik. Preizkusimo ga, da ga vidimo v akciji.

Tukaj smo naredili, da smo od prej vzeli vrata NOR in na izhod uporabili vrata NOR. Kot smo pokazali zgoraj, bodo vrata NOT prevzela vrednost 1 in izvedla 0, vrata NOT pa bodo prevzela vrednost 0 in izvedla 1.

To bo vzelo vrednosti vrat NOR in pretvorilo vse 0s v 1s in 1s v 0s. Tako bo tabela resnice naslednja:

Če želite več prakse pri testiranju teh vrat, lahko sami preizkusite zgornje vrednosti in se prepričajte, da vrata dajejo enakovredne rezultate!

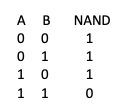

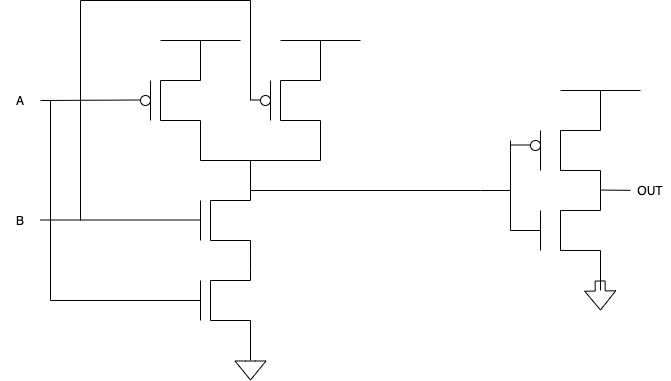

Trdim, da so to vrata NAND, toda preizkusimo tabelo resnic za ta vrata, da ugotovimo, ali so res vrata NAND.

Ko je A 0 in je B 0, bo A-jev pMOS ustvaril 1, A-jev nMOS pa 0; tako bodo ta vrata ustvarila logično 1, saj so povezana z virom z zaprtim vezjem in odklopljena od tal z odprtim vezjem.

Ko je A 0 in je B 1, bo A-jev pMOS ustvaril 1, A-jev nMOS pa 0; tako bodo ta vrata ustvarila logično 1, saj so povezana z virom z zaprtim vezjem in odklopljena od tal z odprtim vezjem.

Ko je A 1 in je B 0, bo B-jev pMOS ustvaril 1, B-jev nMOS pa 0; tako bodo ta vrata ustvarila logično 1, saj so povezana z virom z zaprtim vezjem in odklopljena od tal z odprtim vezjem.

Ko je A 1 in je B 1, bo A-jev pMOS ustvaril 0, A-jev nMOS pa 1; torej moramo preveriti tudi B-jev pMOS in nMOS. B-jev pMOS bo ustvaril 0, B-jev nMOS pa 1; tako bodo ta vrata ustvarila logično 0, saj so odklopljena od vira z odprtim vezjem in povezana z zemljo z zaprtim vezjem.

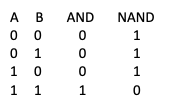

Tabela resnice je naslednja:

Medtem je tabela resnice logične funkcije NAND naslednja:

Tako smo preverili, da so to res vrata NAND.

Zdaj, kako zgradimo vrata IN? No, zgradili bomo vrata IN na enak način, kot smo zgradili vrata ALI iz vrat NOR! Priložili bomo inverter!

Ker smo vse, kar smo naredili, uporabili funkcijo NE na izhodu vrat NAND, bo tabela resnice videti takole:

Še enkrat, preverite, da se prepričate, da je to, kar vam govorim, resnica.

Danes smo obravnavali, kaj so pMOS in nMOS tranzistorji ter kako jih uporabiti za gradnjo bolj zapletenih struktur! Upam, da se vam je ta blog zdel informativen. Če bi radi prebrali moje prejšnje bloge, boste našli spodnji seznam.