izdelki kategorija

- FM oddajnik

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV oddajnik

- 0-50w 50-1kw 2kw-10kw

- FM antene

- TV Antenna

- Antenna pripomočki

- Cable priključek moč Splitter Dummy Load

- RF Transistor

- Napajanje

- avdio oprema

- DTV Front End oprema

- Link sistem

- STL sistem Sistem Mikrovalovna Link

- FM radio

- power Meter

- Ostali izdelki

- Posebno za koronavirus

izdelki Oznake

Fmuser strani

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikanščina

- sq.fmuser.net -> albanski

- ar.fmuser.net -> arabščina

- hy.fmuser.net -> Armenščina

- az.fmuser.net -> azerbajdžanski

- eu.fmuser.net -> baskovščina

- be.fmuser.net -> belorusko

- bg.fmuser.net -> bolgarščina

- ca.fmuser.net -> katalonščina

- zh-CN.fmuser.net -> kitajščina (poenostavljena)

- zh-TW.fmuser.net -> kitajščina (tradicionalno)

- hr.fmuser.net -> hrvaški

- cs.fmuser.net -> češčina

- da.fmuser.net -> danski

- nl.fmuser.net -> nizozemščina

- et.fmuser.net -> estonščina

- tl.fmuser.net -> filipinsko

- fi.fmuser.net -> finski

- fr.fmuser.net -> francosko

- gl.fmuser.net -> galicijščina

- ka.fmuser.net -> gruzijski

- de.fmuser.net -> nemščina

- el.fmuser.net -> grščina

- ht.fmuser.net -> haitijska kreolščina

- iw.fmuser.net -> hebrejščina

- hi.fmuser.net -> hindujščina

- hu.fmuser.net -> madžarščina

- is.fmuser.net -> islandski

- id.fmuser.net -> indonezijski

- ga.fmuser.net -> irski

- it.fmuser.net -> italijanščina

- ja.fmuser.net -> japonski

- ko.fmuser.net -> korejski

- lv.fmuser.net -> latvijski

- lt.fmuser.net -> litovščina

- mk.fmuser.net -> makedonščina

- ms.fmuser.net -> malajščina

- mt.fmuser.net -> malteščina

- no.fmuser.net -> norveščina

- fa.fmuser.net -> perzijski

- pl.fmuser.net -> poljščina

- pt.fmuser.net -> portugalščina

- ro.fmuser.net -> romunščina

- ru.fmuser.net -> ruščina

- sr.fmuser.net -> srbščina

- sk.fmuser.net -> slovaški

- sl.fmuser.net -> slovenščina

- es.fmuser.net -> španščina

- sw.fmuser.net -> svahili

- sv.fmuser.net -> švedščina

- th.fmuser.net -> tajska

- tr.fmuser.net -> turški

- uk.fmuser.net -> ukrajinski

- ur.fmuser.net -> urdujščina

- vi.fmuser.net -> Vietnamščina

- cy.fmuser.net -> valižanščina

- yi.fmuser.net -> jidiš

Kaj je Half Adder: vezje in njegove aplikacije

Date:2021/10/18 21:55:58 Hits:

Half Adder je neke vrste osnovno digitalno vezje. Prej so v analognih vezjih izvajali različne operacije. Po odkritju digitalne elektronike se v njej izvajajo podobne operacije. Digitalni sistemi veljajo za učinkovite in zanesljive. Med različnimi operacijami je ena najpomembnejših operacij aritmetika. Vključuje seštevanje, odštevanje, množenje in deljenje. Vendar pa je že znano, da je to lahko računalnik, vsak elektronski pripomoček, kot je kalkulator, lahko izvaja matematične operacije. Te operacije so sestavljene iz binarnih vrednosti.To je mogoče zaradi prisotnosti določenih vezij v njem. Ta vezja se imenujejo binarni seštevalci in odštevalniki. Ta vrsta vezij je zasnovana za binarne kode, kode Excess-3 in druge kode. Nadaljnji binarni seštevalci so razvrščeni v dve vrsti. To sta: Half Adder in Full Adder Kaj je Half Adder? Postopek dodajanja je enak, edina razlika je izbrani številski sistem. V binarnem sistemu oštevilčevanja obstajata le 0 in 1. Utež števila v celoti temelji na položajih binarnih številk. Med tema 1 in 0 se 1 obravnava kot največja številka, 0 pa kot manjša. Blokovni diagram tega seštevalnika je Polovica seštevalnikaPolovica seštevalnika Diagram polovičnega seštevanja je sestavljen iz dveh vhodov in proizvaja dva izhoda. Velja za najpreprostejša digitalna vezja. Vhodi v to vezje so biti, na katerih je treba seštevanje. Dobljeni rezultati so vsota in prenos.

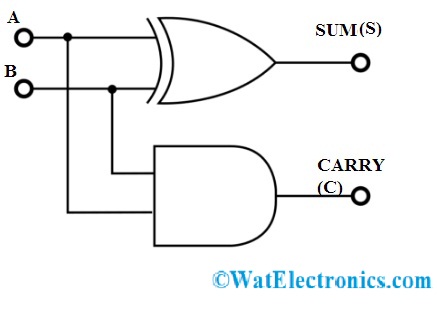

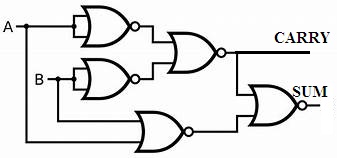

Polovica seštevalnikaPolovica seštevalnika Diagram polovičnega seštevanja je sestavljen iz dveh vhodov in proizvaja dva izhoda. Velja za najpreprostejša digitalna vezja. Vhodi v to vezje so biti, na katerih je treba seštevanje. Dobljeni rezultati so vsota in prenos.  Pol seštevalnika Vezje tega seštevalnika je sestavljeno iz dveh vrat. To so vrata AND in XOR. Uporabljeni vhodi so enaki za vrata, ki so prisotna v vezju. Toda izhod se vzame iz vsakih vrat. Izhod vrat XOR se imenuje SUM, izhod AND pa je znan CARRY. Tabela resnice polovice seštevalnika Za pridobitev razmerja med dobljenim izhodom in uporabljenim vhodom lahko analiziramo tabelo, imenovano Tabela resnic.

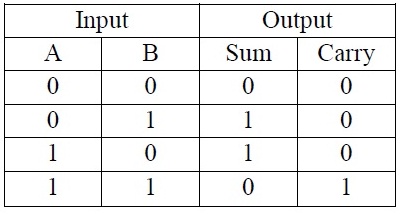

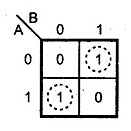

Pol seštevalnika Vezje tega seštevalnika je sestavljeno iz dveh vrat. To so vrata AND in XOR. Uporabljeni vhodi so enaki za vrata, ki so prisotna v vezju. Toda izhod se vzame iz vsakih vrat. Izhod vrat XOR se imenuje SUM, izhod AND pa je znan CARRY. Tabela resnice polovice seštevalnika Za pridobitev razmerja med dobljenim izhodom in uporabljenim vhodom lahko analiziramo tabelo, imenovano Tabela resnic. Tabela resnice polovičnega dodajalca Iz zgornje tabele resničnosti so očitne naslednje točke: Če je A = 0, je B = 0, kar pomeni, da sta oba uporabljena vhoda 0. Potem sta oba izhoda SUM in CARRY 0. Med dvema vhodoma, če kdo vhod je 1, potem bo SUM b e1, CARRY pa 0. Če sta oba vhoda 1, bo SUM enak 0, CARRY pa enak 1. Na podlagi uporabljenih vhodov pol seštevalnik nadaljuje z operacijo enačbo Enačbo za tovrstna vezja je mogoče uresničiti s koncepti vsote izdelkov (SOP) in izdelkov vsote (POS). Logična enačba za to vrsto vezij določa razmerje med uporabljenimi vhodi in pridobljenimi izhodi. Za določitev enačbe se k-karte narišejo na podlagi vrednosti tabele resničnosti. Sestavljen je iz dveh enačb, ker sta v njem uporabljena dva logična vrata. K-zemljevid nosilca je

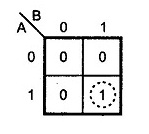

Tabela resnice polovičnega dodajalca Iz zgornje tabele resničnosti so očitne naslednje točke: Če je A = 0, je B = 0, kar pomeni, da sta oba uporabljena vhoda 0. Potem sta oba izhoda SUM in CARRY 0. Med dvema vhodoma, če kdo vhod je 1, potem bo SUM b e1, CARRY pa 0. Če sta oba vhoda 1, bo SUM enak 0, CARRY pa enak 1. Na podlagi uporabljenih vhodov pol seštevalnik nadaljuje z operacijo enačbo Enačbo za tovrstna vezja je mogoče uresničiti s koncepti vsote izdelkov (SOP) in izdelkov vsote (POS). Logična enačba za to vrsto vezij določa razmerje med uporabljenimi vhodi in pridobljenimi izhodi. Za določitev enačbe se k-karte narišejo na podlagi vrednosti tabele resničnosti. Sestavljen je iz dveh enačb, ker sta v njem uporabljena dva logična vrata. K-zemljevid nosilca je  K-Map AND Gate Izhodna enačba funkcije CARRY je pridobljena iz vrat AND.C = A.B Logični izraz za SUM je realiziran z obrazcem SOP. Zato je K-zemljevid za SUM

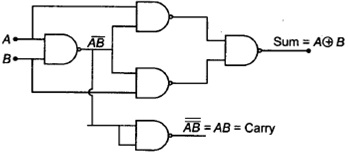

K-Map AND Gate Izhodna enačba funkcije CARRY je pridobljena iz vrat AND.C = A.B Logični izraz za SUM je realiziran z obrazcem SOP. Zato je K-zemljevid za SUM K-zemljevid za vsoto (XOR) Določena enačba je S = A⊕ BAplikacije Uporabe tega osnovnega seštevalnika so naslednje Za izvajanje seštevanja na binarnih bitih aritmetična in logična enota, prisotna v računalniku, raje uporablja to seštevalno vezje. Kombinacija pol seštevalnih vezij vodi do oblikovanja vezja Full Adder. Ta logična vezja so prednostna pri načrtovanju kalkulatorjev. Za izračun naslovov in tabel so ta vezja prednostna. Namesto le dodajanja so ta vezja zmožna obravnavati različne aplikacije v digitalnih vezjih. Nadalje, to postane srce digitalne elektronike. Koda VHDL Koda VHDL za vezje polovičnega dodajalnika je knjižnica ieee; uporabite ieee.std_logic_1164.all; entiteta pol_adder isport (a, b: v bit; vsota, nosi: out bit); konec half_adder ; arhitekturni podatki polovičnega dodajalca isbeginsum <= a xor b; carry <= a in b; končni podatki; FAQs1. Kaj mislite z Adderjem? Digitalna vezja, katerih edini namen je dodajanje, so znana kot seštevalci. To so glavne sestavine ALU. Seštevalniki delujejo poleg različnih formatov številk. Rezultati seštevalnikov so vsota in prenos. Kakšne so omejitve polovičnega seštevalnika? Prenosnega bita, ustvarjenega iz prejšnjega bita, ni mogoče dodati, je omejitev tega seštevalnika. Za izvedbo seštevanja za več bitov teh vezij ni mogoče dati prednost. Kako implementirati polovični seštevalnik z uporabo vrat NOR? Izvedbo te vrste seštevalnika lahko izvedete tudi z vrati NOR. To so še ena Univerzalna vrata.

K-zemljevid za vsoto (XOR) Določena enačba je S = A⊕ BAplikacije Uporabe tega osnovnega seštevalnika so naslednje Za izvajanje seštevanja na binarnih bitih aritmetična in logična enota, prisotna v računalniku, raje uporablja to seštevalno vezje. Kombinacija pol seštevalnih vezij vodi do oblikovanja vezja Full Adder. Ta logična vezja so prednostna pri načrtovanju kalkulatorjev. Za izračun naslovov in tabel so ta vezja prednostna. Namesto le dodajanja so ta vezja zmožna obravnavati različne aplikacije v digitalnih vezjih. Nadalje, to postane srce digitalne elektronike. Koda VHDL Koda VHDL za vezje polovičnega dodajalnika je knjižnica ieee; uporabite ieee.std_logic_1164.all; entiteta pol_adder isport (a, b: v bit; vsota, nosi: out bit); konec half_adder ; arhitekturni podatki polovičnega dodajalca isbeginsum <= a xor b; carry <= a in b; končni podatki; FAQs1. Kaj mislite z Adderjem? Digitalna vezja, katerih edini namen je dodajanje, so znana kot seštevalci. To so glavne sestavine ALU. Seštevalniki delujejo poleg različnih formatov številk. Rezultati seštevalnikov so vsota in prenos. Kakšne so omejitve polovičnega seštevalnika? Prenosnega bita, ustvarjenega iz prejšnjega bita, ni mogoče dodati, je omejitev tega seštevalnika. Za izvedbo seštevanja za več bitov teh vezij ni mogoče dati prednost. Kako implementirati polovični seštevalnik z uporabo vrat NOR? Izvedbo te vrste seštevalnika lahko izvedete tudi z vrati NOR. To so še ena Univerzalna vrata. Polovica seštevalnika, ki uporablja vrata NOR4. Kako implementirati Half Adder z uporabo vrat NAND? Vrata NAND so ena od vrst univerzalnih vrat. Kaže, da je z uporabo vrat NAND možno oblikovanje kakršnih koli vezij.

Polovica seštevalnika, ki uporablja vrata NOR4. Kako implementirati Half Adder z uporabo vrat NAND? Vrata NAND so ena od vrst univerzalnih vrat. Kaže, da je z uporabo vrat NAND možno oblikovanje kakršnih koli vezij. Polovica seštevalnika Iz zgornjega vezja je mogoče prenosni izhod ustvariti z uporabo izhoda enega vrata NAND na vhod kot druga vrata NAND. To je nič drugega kot znano izhodu, pridobljenemu iz vrat AND. Izhodno enačbo SUM je mogoče ustvariti z uporabo izhoda začetnih vrat NAND skupaj s posameznimi vhodi A in B za nadaljnja vrata NAND. Končno se rezultati, pridobljeni s temi vrati NAND, znova uporabijo na vratih. Tako se generira izhod za SUM. Zato je mogoče osnovni seštevalnik v digitalnem vezju oblikovati z uporabo različnih logičnih vrat. Toda seštevanje več bitov se zaplete in velja za omejitev polovičnega seštevalnika. Ali lahko opišete, kateri IC se uporablja za operacijo prirastka v katerem koli praktičnem števcu?

Polovica seštevalnika Iz zgornjega vezja je mogoče prenosni izhod ustvariti z uporabo izhoda enega vrata NAND na vhod kot druga vrata NAND. To je nič drugega kot znano izhodu, pridobljenemu iz vrat AND. Izhodno enačbo SUM je mogoče ustvariti z uporabo izhoda začetnih vrat NAND skupaj s posameznimi vhodi A in B za nadaljnja vrata NAND. Končno se rezultati, pridobljeni s temi vrati NAND, znova uporabijo na vratih. Tako se generira izhod za SUM. Zato je mogoče osnovni seštevalnik v digitalnem vezju oblikovati z uporabo različnih logičnih vrat. Toda seštevanje več bitov se zaplete in velja za omejitev polovičnega seštevalnika. Ali lahko opišete, kateri IC se uporablja za operacijo prirastka v katerem koli praktičnem števcu?

Pustite sporočilo

Seznam sporočilo

Komentarji Nalaganje ...