izdelki kategorija

- FM oddajnik

- 0-50w 50w-1000w 2kw-10kw 10kw +

- TV oddajnik

- 0-50w 50-1kw 2kw-10kw

- FM antene

- TV Antenna

- Antenna pripomočki

- Cable priključek moč Splitter Dummy Load

- RF Transistor

- Napajanje

- avdio oprema

- DTV Front End oprema

- Link sistem

- STL sistem Sistem Mikrovalovna Link

- FM radio

- power Meter

- Ostali izdelki

- Posebno za koronavirus

izdelki Oznake

Fmuser strani

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> afrikanščina

- sq.fmuser.net -> albanski

- ar.fmuser.net -> arabščina

- hy.fmuser.net -> Armenščina

- az.fmuser.net -> azerbajdžanski

- eu.fmuser.net -> baskovščina

- be.fmuser.net -> belorusko

- bg.fmuser.net -> bolgarščina

- ca.fmuser.net -> katalonščina

- zh-CN.fmuser.net -> kitajščina (poenostavljena)

- zh-TW.fmuser.net -> kitajščina (tradicionalno)

- hr.fmuser.net -> hrvaški

- cs.fmuser.net -> češčina

- da.fmuser.net -> danski

- nl.fmuser.net -> nizozemščina

- et.fmuser.net -> estonščina

- tl.fmuser.net -> filipinsko

- fi.fmuser.net -> finski

- fr.fmuser.net -> francosko

- gl.fmuser.net -> galicijščina

- ka.fmuser.net -> gruzijski

- de.fmuser.net -> nemščina

- el.fmuser.net -> grščina

- ht.fmuser.net -> haitijska kreolščina

- iw.fmuser.net -> hebrejščina

- hi.fmuser.net -> hindujščina

- hu.fmuser.net -> madžarščina

- is.fmuser.net -> islandski

- id.fmuser.net -> indonezijski

- ga.fmuser.net -> irski

- it.fmuser.net -> italijanščina

- ja.fmuser.net -> japonski

- ko.fmuser.net -> korejski

- lv.fmuser.net -> latvijski

- lt.fmuser.net -> litovščina

- mk.fmuser.net -> makedonščina

- ms.fmuser.net -> malajščina

- mt.fmuser.net -> malteščina

- no.fmuser.net -> norveščina

- fa.fmuser.net -> perzijski

- pl.fmuser.net -> poljščina

- pt.fmuser.net -> portugalščina

- ro.fmuser.net -> romunščina

- ru.fmuser.net -> ruščina

- sr.fmuser.net -> srbščina

- sk.fmuser.net -> slovaški

- sl.fmuser.net -> slovenščina

- es.fmuser.net -> španščina

- sw.fmuser.net -> svahili

- sv.fmuser.net -> švedščina

- th.fmuser.net -> tajska

- tr.fmuser.net -> turški

- uk.fmuser.net -> ukrajinski

- ur.fmuser.net -> urdujščina

- vi.fmuser.net -> Vietnamščina

- cy.fmuser.net -> valižanščina

- yi.fmuser.net -> jidiš

Kaj je pol-odštevalec: delo in njegove aplikacije, K-MAP, vezje z uporabo vrat NAND

Date:2021/10/18 21:55:58 Hits:

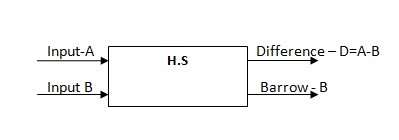

Za obdelavo informacij, kot sta svetloba ali zvok, od ene do druge točke lahko uporabimo analogna vezja z ustreznimi vhodi v obliki analognih signalov. V tem procesu obstaja možnost, da vhodni analogni signali poberejo šum, kar lahko privede do izgube izhodnega signala, kar pomeni, da ne glede na vhod, ki ga obdelujemo na vhodni ravni, ni enak izhodni stopnji. Za premagovanje teh digitalnih vezij se izvajajo. Digitalno vezje je lahko zasnovano z logičnimi vrati. Logična vrata so elektronsko vezje, ki izvaja logične operacije na podlagi svojih vhodov in daje izhodu samo en bit, bodisi nizek (logika 0 = ničelna napetost) ali visok (logika 1 = visoka napetost). Kombinacijska vezja so lahko zasnovana z več logičnimi vrati. Ta vezja so hitra in časovno neodvisna, brez povratnih informacij med vhodom in izhodom. Kombinacijska vezja so uporabna za aritmetične in logične operacije. Najboljši primeri kombinacijskih vezij so pol seštevalnik, polni seštevalec, pol odštevalnik, polni odštevalec, multiplekserji, demultiplekserji, dajalnik in dekoder. Kaj je pol odštevalec? se uporablja za odštevanje dveh bitov od vhoda. Tukaj je rezultat odštevalnika popolnoma odvisen od trenutnih vhodov in ni odvisen od prejšnjih stopenj. Izhodi pol-odštevalnika so razlika in barrow. Podobno je arthimetic odštevanju, kjer bi, če je odštevalec večji od minuenda, odšli po izposojo B = 1, sicer bi izposoja ostala nič B = 0. Za boljše razumevanje pojdimo na spodnjo tabelo resnice.  pol-odštevalec-blok-diagram Tabela resnice Tabela resnice polovičnega odštevalnika prikazuje izhodne vrednosti glede na vhode, ki se uporabljajo na vhodnih stopnjah. Tabela resnice je razdeljena na dva dela. Levi del je označen kot vhodna stopnja, desni pa kot izhodna stopnja.V digitalnih vezjih vhod 0 in vhod 1 označujeta nizko logiko in visoko visoko logiko. Glede na konfiguracijo logično nizko pomeni ničelno napetost, visoko logično visoko napetost (na primer 5V, 7V, 12V itd.). Vhodi Izhodi Vhod -AI Vhod -B Razlika -DBarrow -B 000010 1001111100 Tabela resnice Pojasnilo Ko sta vhoda A in B nič, sta tudi izhoda polovičnega odštevalnika D in B enaka. Barrow je nič Ko je vhod A nič in vhod B visok, so izhodi D in B visoki z ustreznimi. Ko sta oba vhoda visoka, sta oba izhoda polovičnega odštevalnika nič. Iz zgornje tabele resničnosti lahko poiščite enačbo za razliko (D) in Barrow (B). Enačbe za razliko-D: razlika je velika, če so vhodi A = 1, B = 1 in A = 0, B = 0. Iz te trditve je D = AB '+A'B = A⊕B. V skladu z enačbo D označuje Ex-or gate.D = A⊕BEquations za Barrow-B: Barro je visok le, če je vhod A nizek in B visok. Od te točke bo enačba za Barrow B, B = A'BB = A'B Iz zgornjih razlik in enačb barrow lahko oblikujemo vezje polovičnega odštevalnika z uporabo K -MapK -MapKarnaugh zemljevid poenostavi izraz Boolove algebre za pol vezja odštevalnika. To je uradna metoda za iskanje enačbe Boolove algebre za katero koli vezje. Rešimo Boolove izraze za vezje polovičnega odštevalnika s pomočjo K-zemljevida. K-zemljevid za razliko (D) in Barrow (B)

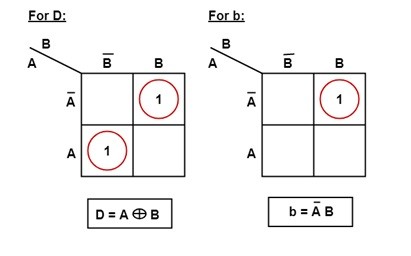

pol-odštevalec-blok-diagram Tabela resnice Tabela resnice polovičnega odštevalnika prikazuje izhodne vrednosti glede na vhode, ki se uporabljajo na vhodnih stopnjah. Tabela resnice je razdeljena na dva dela. Levi del je označen kot vhodna stopnja, desni pa kot izhodna stopnja.V digitalnih vezjih vhod 0 in vhod 1 označujeta nizko logiko in visoko visoko logiko. Glede na konfiguracijo logično nizko pomeni ničelno napetost, visoko logično visoko napetost (na primer 5V, 7V, 12V itd.). Vhodi Izhodi Vhod -AI Vhod -B Razlika -DBarrow -B 000010 1001111100 Tabela resnice Pojasnilo Ko sta vhoda A in B nič, sta tudi izhoda polovičnega odštevalnika D in B enaka. Barrow je nič Ko je vhod A nič in vhod B visok, so izhodi D in B visoki z ustreznimi. Ko sta oba vhoda visoka, sta oba izhoda polovičnega odštevalnika nič. Iz zgornje tabele resničnosti lahko poiščite enačbo za razliko (D) in Barrow (B). Enačbe za razliko-D: razlika je velika, če so vhodi A = 1, B = 1 in A = 0, B = 0. Iz te trditve je D = AB '+A'B = A⊕B. V skladu z enačbo D označuje Ex-or gate.D = A⊕BEquations za Barrow-B: Barro je visok le, če je vhod A nizek in B visok. Od te točke bo enačba za Barrow B, B = A'BB = A'B Iz zgornjih razlik in enačb barrow lahko oblikujemo vezje polovičnega odštevalnika z uporabo K -MapK -MapKarnaugh zemljevid poenostavi izraz Boolove algebre za pol vezja odštevalnika. To je uradna metoda za iskanje enačbe Boolove algebre za katero koli vezje. Rešimo Boolove izraze za vezje polovičnega odštevalnika s pomočjo K-zemljevida. K-zemljevid za razliko (D) in Barrow (B) K-zemljevid za razliko (D) in Barrow (B) Po K-karti je prvi implikant A'B, drugi implikant pa AB'. Ko poenostavimo ta dva enačba implikantov, bomo dobili poenostavljeno enačbo za razliko DD = A'B+AB'Tada je D = A⊕B. Ta enačba preprosto označuje vrata Ex-OR.Če želimo poiskati poenostavljen Boolean izraz za barrow B, moramo slediti istemu postopku, ki smo ga upoštevali pri Difference D. Zato je B = A'B. NOR vrata se imenujejo univerzalna. Tu se vrata NAND imenujejo univerzalna vrata, ker lahko oblikujemo katero koli vrsto digitalnega vezja z uporabo n številčnih kombinacij vrat NAND. Zaradi te posebnosti se vrata NAND imenujejo univerzalna vrata. Zdaj oblikujemo vezje polovičnega odštevalnika z uporabo vrat NAND.

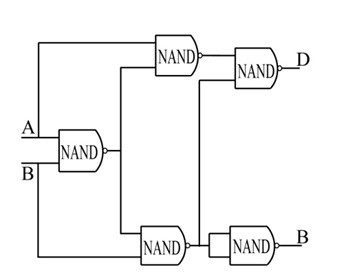

K-zemljevid za razliko (D) in Barrow (B) Po K-karti je prvi implikant A'B, drugi implikant pa AB'. Ko poenostavimo ta dva enačba implikantov, bomo dobili poenostavljeno enačbo za razliko DD = A'B+AB'Tada je D = A⊕B. Ta enačba preprosto označuje vrata Ex-OR.Če želimo poiskati poenostavljen Boolean izraz za barrow B, moramo slediti istemu postopku, ki smo ga upoštevali pri Difference D. Zato je B = A'B. NOR vrata se imenujejo univerzalna. Tu se vrata NAND imenujejo univerzalna vrata, ker lahko oblikujemo katero koli vrsto digitalnega vezja z uporabo n številčnih kombinacij vrat NAND. Zaradi te posebnosti se vrata NAND imenujejo univerzalna vrata. Zdaj oblikujemo vezje polovičnega odštevalnika z uporabo vrat NAND. pol-odštevalec-izveden-z-NAND-vrati Vzpostavimo lahko vezje polovičnega odštevalnika s petimi vrati NAND.A in B upoštevamo kot vhoda na prvo stopnjo vrat NAND, njegov izhod je spet priključen kot en vhod na druga vrata NAND kot tudi tretja vrata NAND. V skladu z njihovimi vhodi daje izhod, na zadnji stopnji iz vrat NAND pa bosta na izhodu razlika izhoda D in izhoda B B. Končna izhodna enačba D je D = A ⊕B in enačba Browrow B kot B = A'B. Z uporabo različne kombinacije vrat NAND za konstrukcijo pol-odštevalnika bodo končne enačbe razlike in barow le D = A⊕B in B = A'B. pol odštevalnika Obstajajo različne aplikacije teh odštevalnikov. Praktično jih je enostavno analizirati. Nekateri izmed njih so navedeni na naslednji način. Če želite odšteti številke, ki so v najmanjšem položaju pri stolpcih, so ti odštevalniki prednostni. Aritmetična in logična enota (ALU), ki je prisotna v procesorju, raje uporablja to enoto za odštevanje. Da bi zmanjšali popačenja v zvoku na podlagi zahtevane operacije ima pol odštevalnik možnost povečati ali zmanjšati število operaterjev. Pol odštevalnikov se uporablja v ojačevalniku. Med oddajanjem zvočnih signalov se ti uporabljajo za preprečevanje popačenj. Pol vezja odštevalnika. V pogojih v realnem času odštevanja več števil bitov ni mogoče izvesti z uporabo polovičnih odštevalnikov. To pomanjkljivost lahko odpravite z uporabo celotnega odštevalnika.

pol-odštevalec-izveden-z-NAND-vrati Vzpostavimo lahko vezje polovičnega odštevalnika s petimi vrati NAND.A in B upoštevamo kot vhoda na prvo stopnjo vrat NAND, njegov izhod je spet priključen kot en vhod na druga vrata NAND kot tudi tretja vrata NAND. V skladu z njihovimi vhodi daje izhod, na zadnji stopnji iz vrat NAND pa bosta na izhodu razlika izhoda D in izhoda B B. Končna izhodna enačba D je D = A ⊕B in enačba Browrow B kot B = A'B. Z uporabo različne kombinacije vrat NAND za konstrukcijo pol-odštevalnika bodo končne enačbe razlike in barow le D = A⊕B in B = A'B. pol odštevalnika Obstajajo različne aplikacije teh odštevalnikov. Praktično jih je enostavno analizirati. Nekateri izmed njih so navedeni na naslednji način. Če želite odšteti številke, ki so v najmanjšem položaju pri stolpcih, so ti odštevalniki prednostni. Aritmetična in logična enota (ALU), ki je prisotna v procesorju, raje uporablja to enoto za odštevanje. Da bi zmanjšali popačenja v zvoku na podlagi zahtevane operacije ima pol odštevalnik možnost povečati ali zmanjšati število operaterjev. Pol odštevalnikov se uporablja v ojačevalniku. Med oddajanjem zvočnih signalov se ti uporabljajo za preprečevanje popačenj. Pol vezja odštevalnika. V pogojih v realnem času odštevanja več števil bitov ni mogoče izvesti z uporabo polovičnih odštevalnikov. To pomanjkljivost lahko odpravite z uporabo celotnega odštevalnika.

Pustite sporočilo

Seznam sporočilo

Komentarji Nalaganje ...